浏览量:32773 发布日期:2021.09.24

1、以太网接口介绍:

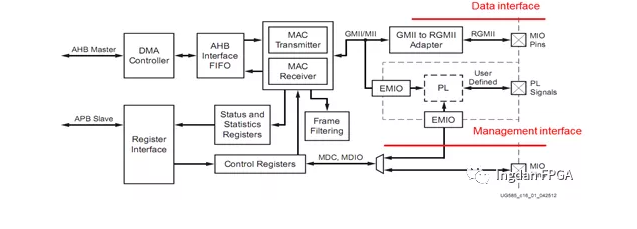

以太网接口包含管理、数据通信接口,管理接口也就是我们常说的MDC/MDIO,用来访问phy寄存器,配置工作模式、检测工作状态。数据接口:常见的有MII, GMII, RGMII,SGMII, QSGMII等,我们本次专注在RGMII。

TX/RX data between MAC & PHY

帧格式: CL22(GE), CL45(XE);

Preamble (32bits) | Start (2bits) | OP Code (2bits) | PHYAD (5bits) | REGAD (5bits) | Turn Around (2bits) | Data (16bits) | Idle | |

Read | 1.......1 | 01 | 10 | A4A3A2A1A0 | R4R3R2R1R0 | Z0 | D15.......D0 | Z* |

Write | 1.......1 | 01 | 01 | A4A3A2A1A0 | R4R3R2R1R0 | 10 | D15.......D0 | Z* |

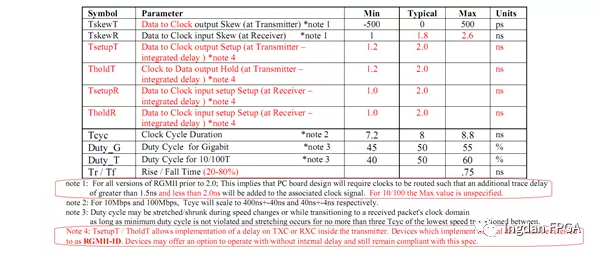

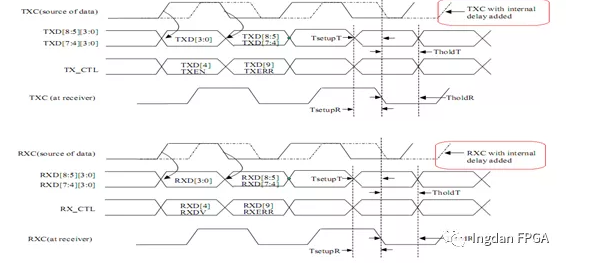

RGMII规范中约定data和clock之间需要有2ns延迟,实现方式:

A. PCB板上绕线实现 (不推荐);

B. PCB(data/clock等长处理)+PHY芯片上分别设置TX/RX delay(现在phy基本上均支持,使用前请查看phy手册确认);

RGMII规范约定:

带有internal delay的phy/mac:

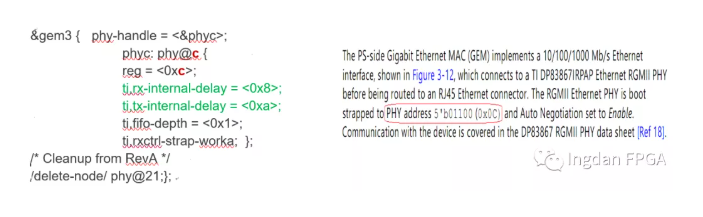

Linux如何配置phy地址&phy delay,以ZCU102为例,GEM3 phy address=0xC,采用phy internal tx/rx delay,在设备树system-usr.dsti中添加phy地址和delay(有的phy硬件配置好,无需额外添加)。