浏览量:32771 发布日期:2021.10.27

此前,我们在SelectIO简介连载一中介绍了其架构,本章会继续介绍如何使用其gearbox功能来实现不同的比率的串并转换功能。

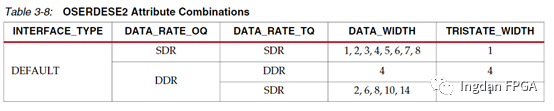

7 Series FPGA中LVDS使用了ISERDESE2,SDR Rate可设为2,3,4,5,6,7,8。DDR Rate可设为4,6,8,10,14。

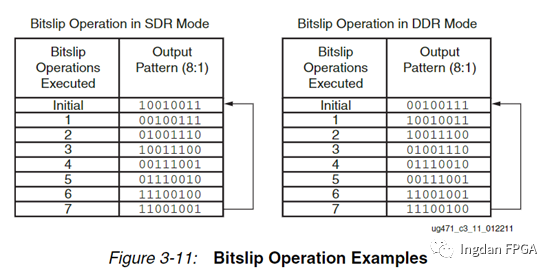

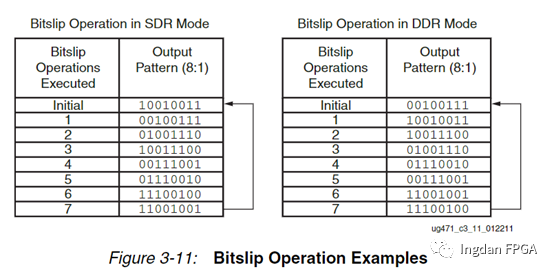

从UG471的Bitslip部分可以看出在SDR和DDR移位的位数不一样。在SDR模式下,一个Bitslip脉冲使数据左移一位;而在DDR模式下,一个Bitslip脉冲使数据右移一位或左移三位。

所以在某些传输过程中,可以先传预设值,等待接收方调整Idelay和Bitslip解出正确的预设值后再传输有效数据。

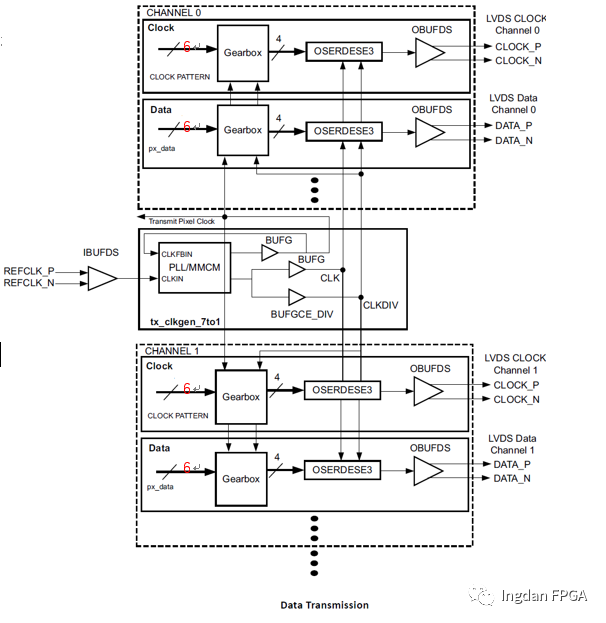

对习惯使用7 Series FPGA用户在接触Xilinx®UltraScale™和UltraScale +™器件 SelectIO时感觉不习惯,原因Xilinx®UltraScale™和UltraScale +™是ISERDESE3和OSERDESE3组件,使用Select IO需要在IP catlog中选择high_speed_selectio IP Configuration interface 在Serialization Factor选项中只有8或者4可以选择。

在Pin Selection选择时会发现IO选择会有一定限制,在Sensor的应用中HP bank理想的硬件设计是在同一个bank中连续放置设备I/O,部分Sensor输出的Serialization Factor需要7:1,6:1,5:1,不能直接使用ISERDES。

对这类应用Xilinx 提供了XAPP1315 7:1的参考设计,那么对6:1,5:1这种应用用户需要在参考设计上改哪里,怎样去改?

下面我们提供修改方式供参考。

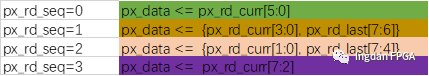

1、从Data Reception看需要把ISERDESE3 输出的8位数据(Serialization Factor=8)通过gearbox模块转成7,6,5位的数据。其中7位的数据XAPP1315已经做过了,这里我们用6:1的数据为例, 需要从ISERDES3实现Read8 bit 数据通过gearbox 转换为6bit数据。

2、对于Read 8 to 6 gearbox设计方式:

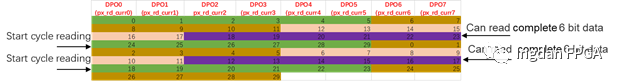

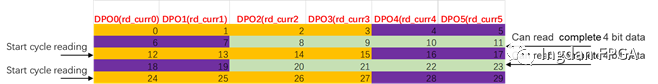

从数据排列可以分析到8 bit数据在每次读取6 bit数据,经过4次后开始循环,我们通过状态机设计gearbox的代码需只需要实现;

// Read 8 to 6 gearbox

//

always @ (posedge px_clk)

begin

case (px_rd_seq )

3'h0 : begin

px_data <=px_rd_curr[5:0];

end

3'h1 : begin

px_data <={px_rd_curr[3:0], px_rd_last[7:6]};

end

3'h2 : begin

px_data <={px_rd_curr[1:0], px_rd_last[7:4]};

end

3'h3 : begin

px_data <={px_rd_last[7:2]};

end

endcase

end

3、Data Transmission,OSERDES3使用4 bit 输入,参考例程是把ISERDES的数据接到OSERDES,这里我们在参考例程上任然使用ISERDE 到OSERDES的数据传送方式验证。分析知道需要一个6 bit 转4 bit数据的 Gearbox。

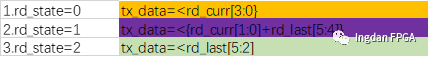

4、Gearbox设计思路是把6 bit的数据按4bit大小去读取直到数据开始循环。

通过表格客户分析出设计代码做3次循环可以满足要求

Read state machine and gear box

//

always @ (posedge tx_clkdiv4)

begin

if(!tx_enable) begin

rd_addr <= 4'b0;

rd_state <= 3'h0;

end else begin

case (rd_state )

3'h0 : begin